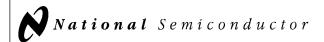

# ADC1242 12-Bit Plus Sign Sampling A/D Converter

# **General Description**

The ADC1242 is a CMOS 12-bit plus sign successive approximation analog-to-digital converter. On request, the ADC1242 goes through a self-calibration cycle that adjusts positive linearity error to less than  $\pm 1$  LSB full-scale error to less than  $\pm 3$  LSB, and zero error to less than  $\pm 2$  LSB. The ADC1242 also has the ability to go through an Auto-Zero cycle that corrects the zero error during every conversion.

The analog input to the ADC1242 is tracked and held by the internal circuitry, and therefore does not require an external sample-and-hold. A unipolar analog input voltage range (0V to  $\pm$ 5V) or a bipolar range ( $\pm$ 5V) can be accommodated with  $\pm$ 5V supplies.

The 13-bit word on the outputs of the ADC1242 gives a 2's complement representation of negative numbers. The digital inputs and outputs are compatible with TTL or CMOS logic levels.

# **Applications**

- Digital Signal Processing

- High Resolution Process Control

- Instrumentation

# **Key Specifications**

■ Resolution 12 Bits plus Sign

■ Conversion Time 13.8 μs (max)

■ Linearity Error ±1 LSB (± 0.0244%) (max)

■ Zero Error ±2 LSB (max)

■ Positive Full Scale Error ±3 LSB (max)

■ Power Consumption 70 mW (max)

#### **Features**

- Self-calibrating

- Internal sample-and-hold

- Bipolar input range with ±5V supplies and single +5V reference

- No missing codes over temperature

- TTL/MOS input/output compatible

- Standard 28-pin ceramic DIP

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

# Absolute Maximum Ratings (Notes 1 & 2)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications.

Supply Voltage ( $V_{CC} = DV_{CC} = AV_{CC}$ ) 6.5V Negative Supply Voltage ( $V^-$ ) -6.5V Voltage at Logic Control Inputs -0.3V to ( $V_{CC} + 0.3V$ ) Voltage at Analog Input ( $V_{IN}$ ) ( $V^-$  -0.3V) to ( $V_{CC} + 0.3V$ ) AV $_{CC}$ -DV $_{CC}$  (Note 7) 0.3V Input Current at any Pin (Note 3)  $\pm 5$  mA Package Input Current (Note 3)  $\pm 20$  mA Power Dissipation at 25°C (Note 4) 875 mW Storage Temperature Range -65°C to +150°C

ESD Susceptability (Note 5) 2000V

Soldering Information

J Package (10 seconds) 300°C

# Operating Ratings (Notes 1 and 2)

Temperature Range  $T_{MIN} \le T_A \le T_{MAX}$   $-40^{\circ}C \le T_A \le +85^{\circ}C$   $DV_{CC}$  and  $AV_{CC}$  Voltage (Notes 6 and 7) 4.5V to 5.5V  $Negative Supply Voltage (V^-)$  -4.5V to -5.5V Reference Voltage  $(V_{REF}, Notes 6 and 7)$  3.5V to  $AV_{CC} + 50$  mV

# **Converter Electrical Characteristics**

The following specifications apply for  $V_{CC} = DV_{CC} = AV_{CC} = +5.0V$ ,  $V^- = -5.0V$ ,  $V_{REF} = +4.096V$ , and  $f_{CLK} = 2.0$  MHz unless otherwise specified. **Boldface limits apply for T\_A = T\_J = T\_{MIN} to T\_{MAX}**; all other limits  $T_A = T_J = 25^{\circ}C$ . (Notes 6, 7 and 8)

| Symbol           | Parame                                                   | ter                  | Conditions                                           | Typical<br>(Note 9) | Limit<br>(Notes 10, 18)                         | Units<br>(Limit)  |

|------------------|----------------------------------------------------------|----------------------|------------------------------------------------------|---------------------|-------------------------------------------------|-------------------|

| STATIC C         | HARACTERISTICS                                           |                      |                                                      |                     |                                                 |                   |

|                  | Positive Integral<br>Linearity Error                     |                      | After Auto-Cal<br>(Notes 11 and 12)                  |                     | ± 1                                             | LSB(max)          |

|                  | Differential Linearity                                   |                      | After Auto-Cal (Notes 11 and 12)                     | 12<br>±2            | Bits(min)                                       |                   |

|                  | Zero Error                                               |                      | After Auto-Zero or Auto-Cal (Notes 12 and 13)        |                     | LSB(max)                                        |                   |

|                  | Positive and Negative Full-                              | -Scale Error         | After Auto-Cal (Note 12)                             |                     | ± 3                                             | LSB(max)          |

| C <sub>REF</sub> | V <sub>REF</sub> Input Capacitance                       |                      |                                                      | 80                  |                                                 | pF                |

| C <sub>IN</sub>  | Analog Input Capacitance                                 |                      |                                                      | 65                  |                                                 | pF                |

| V <sub>IN</sub>  | Analog Input Voltage                                     |                      |                                                      |                     | V <sup>-</sup> - 0.05<br>V <sub>CC</sub> + 0.05 | V(min)<br>V(max)  |

|                  | Power Supply                                             | Zero Error (Note 14) | $AV_{CC} = DV_{CC} = 5V \pm 5\%,$                    | ± 1/8               |                                                 | LSB               |

|                  | Sensitivity                                              | Full-Scale Error     | $V_{REF} = 4.75V, V^{-} = -5V \pm 5\%$               | ± 1/8               |                                                 | LSB               |

|                  |                                                          | Linearity Error      |                                                      | ± 1/8               |                                                 | LSB               |

| DYNAMIC          | CHARACTERISTICS                                          |                      |                                                      |                     |                                                 |                   |

| S/(N+D)          | Unipolar Signal-to-Noise + Distortion<br>Ratio (Note 17) |                      | $f_{IN} = 1 \text{ kHz}, V_{IN} = 4.85 V_{p-p}$      | 72                  |                                                 | dB                |

|                  |                                                          |                      | $f_{IN} = 10 \text{ kHz}, V_{IN} = 4.85 V_{p-p}$     | 72                  |                                                 | dB                |

| S/(N+D)          | Bipolar Signal-to-Noise + Distortion<br>Ratio (Note 17)  |                      | $f_{IN} = 1 \text{ kHz}, V_{IN} = \pm 4.85 V_{p-p}$  | 76                  |                                                 | dB                |

|                  |                                                          |                      | $f_{IN} = 10 \text{ kHz}, V_{IN} = \pm 4.85 V_{p-p}$ | 76                  |                                                 | dB                |

|                  | Unipolar Full Power Bandwidth (Note 17)                  |                      | $V_{IN} = 0V$ to 4.85V                               | 32                  |                                                 | kHz               |

|                  | Bipolar Full Power Bandwidth (Note 17)                   |                      | $V_{IN} = \pm 4.85 V_{p-p}$                          | 25                  |                                                 | kHz               |

| t <sub>Ap</sub>  | t <sub>Ap</sub> Aperture Time                            |                      |                                                      | 100                 |                                                 | ns                |

|                  | Aperture Jitter                                          |                      |                                                      | 100                 |                                                 | ps <sub>rms</sub> |

**Digital and DC Electrical Characteristics**The following specifications apply for  $V_{CC} = DV_{CC} = AV_{CC} = +5.0V$ ,  $V^- = -5.0V$ ,  $V_{REF} = +4.096V$ , and  $f_{CLK} = 2.0$  MHz unless otherwise specified. **Boldface limits apply for T<sub>A</sub> = T<sub>J</sub> = T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (Notes 6 and 7)

| Symbol              | Parameter                                                 | Condition                                                             | Typical<br>(Note 9) | Limit<br>(Notes 10, 18) | Units<br>(Limits) |  |

|---------------------|-----------------------------------------------------------|-----------------------------------------------------------------------|---------------------|-------------------------|-------------------|--|

| V <sub>IN(1)</sub>  | Logical "1" Input Voltage for<br>All Inputs except CLK IN | V <sub>CC</sub> = 5.25V                                               |                     | 2.0                     | V(min)            |  |

| V <sub>IN(0)</sub>  | Logical "0" Input Voltage for<br>All Inputs except CLK IN | V <sub>CC</sub> = 4.75V                                               |                     | 0.8                     | V(max)            |  |

| I <sub>IN(1)</sub>  | Logical "1" Input Current                                 | V <sub>IN</sub> = 5V                                                  | 0.005               | 1                       | μA(max)           |  |

| I <sub>IN(0)</sub>  | Logical "0" Input Current                                 | $V_{IN} = 0V$                                                         | -0.005              | <b>-1</b>               | μA(max)           |  |

| $V_T^+$             | CLK IN Positive-Going<br>Threshold Voltage                |                                                                       | 2.8                 | 2.7                     | V(min)            |  |

| $V_T^-$             | CLK IN Negative-Going<br>Threshold Voltage                | 2.3                                                                   | V(max)              |                         |                   |  |

| V <sub>H</sub>      | CLK IN Hysteresis $[V_T^+(min) - V_T^-(max)]$             |                                                                       | 0.7                 | 0.4                     | V(min)            |  |

| V <sub>OUT(1)</sub> | Logical "1" Output Voltage                                | $V_{CC} = 4.75V$ :<br>$I_{OUT} = -360 \mu A$<br>$I_{OUT} = -10 \mu A$ |                     | 2.4<br>4.5              | V(min)<br>V(min)  |  |

| V <sub>OUT(0)</sub> | Logical "0" Output Voltage                                | $V_{CC} = 4.75V$ $I_{OUT} = 1.6 \text{ mA}$                           |                     | 0.4                     | V(max)            |  |

| lout                | TRI-STATE® Output Leakage                                 | V <sub>OUT</sub> = 0V                                                 | -0.01               | -3                      | μA(max)           |  |

|                     | Current                                                   | V <sub>OUT</sub> = 5V                                                 | 0.01                | 3                       | μA(max)           |  |

| I <sub>SOURCE</sub> | Output Source Current                                     | V <sub>OUT</sub> = 0V                                                 | -20                 | -6.0                    | mA(min)           |  |

| I <sub>SINK</sub>   | Output Sink Current                                       | V <sub>OUT</sub> = 5V                                                 | 20                  | 8.0                     | mA(min)           |  |

| DI <sub>CC</sub>    | DV <sub>CC</sub> Supply Current                           | $f_{CLK} = 2 \text{ MHz}, \overline{CS} = "1"$                        | 1                   | 2                       | mA(max)           |  |

| Al <sub>CC</sub>    | AV <sub>CC</sub> Supply Current                           | $f_{CLK} = 2 \text{ MHz}, \overline{CS} = "1"$                        | 2.8                 | 6                       | mA(max)           |  |

| 1-                  | V- Supply Current                                         | $f_{CLK} = 2 \text{ MHz}, \overline{CS} = "1"$                        | 2.8                 | 6                       | mA(max)           |  |

# **AC Electrical Characteristics**

The following specifications apply for DV<sub>CC</sub> = AV<sub>CC</sub> = +5.0V, V<sup>-</sup> = -5.0V, t<sub>r</sub> = t<sub>f</sub> = 20 ns unless otherwise specified. **Boldface limits apply for T<sub>A</sub>** = **T<sub>J</sub>** = **T<sub>MIN</sub> to T<sub>MAX</sub>**; all other limits T<sub>A</sub> = T<sub>J</sub> = 25°C. (Notes 6 and 7)

| Symbol                            | Parameter                                                                | Conditions                                                                         | Typical<br>(Note 9)           | Limit<br>(Notes 10, 18)          | Units<br>(Limits)           |

|-----------------------------------|--------------------------------------------------------------------------|------------------------------------------------------------------------------------|-------------------------------|----------------------------------|-----------------------------|

| f <sub>CLK</sub>                  | Clock Frequency                                                          |                                                                                    | 0.5<br>4.0                    | 2.0                              | MHz<br>MHz(min)<br>MHz(max) |

|                                   | Clock Duty Cycle                                                         |                                                                                    | 50                            | 40<br>60                         | %<br>%(min)<br>%(max)       |

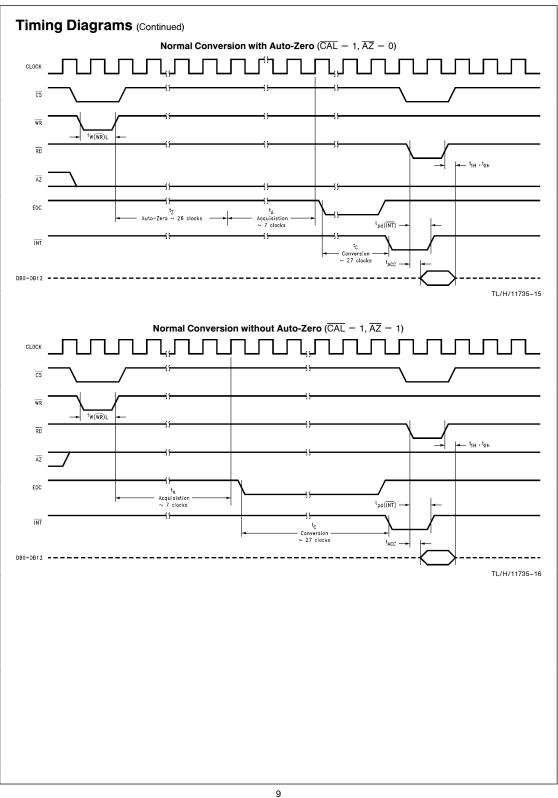

| t <sub>C</sub>                    | Conversion Time                                                          |                                                                                    | 27(1/f <sub>CLK</sub> )       | 27(1/f <sub>CLK</sub> ) + 300 ns | (max)                       |

|                                   |                                                                          | f <sub>CLK</sub> = 2.0 MHz                                                         | 13.5                          |                                  | μs                          |

| t <sub>A</sub>                    | Acquisition Time (Note 15)                                               | $R_{SOURCE} = 50\Omega$<br>$f_{CLK} = 2.0 \text{ MHz}$                             | 7(1/f <sub>CLK</sub> )<br>3.5 | 7(1/f <sub>CLK</sub> ) + 300 ns  | (max)<br>μs                 |

| t <sub>Z</sub>                    | Auto Zero Time                                                           |                                                                                    | 26                            | 26                               | 1/f <sub>CLK</sub> (max)    |

|                                   |                                                                          | f <sub>CLK</sub> = 2.0 MHz                                                         | 13                            |                                  | μs                          |

| tCAL                              | Calibration Time                                                         |                                                                                    | 1396                          |                                  | 1/f <sub>CLK</sub>          |

|                                   |                                                                          | f <sub>CLK</sub> = 2.0 MHz                                                         | 698                           | 706                              | μs(max)                     |

| tw( <del>CAL</del> )L             | Calibration Pulse Width                                                  | (Note 16)                                                                          | 60                            | 200                              | ns(min)                     |

| tw(WR)L                           | Minimum WR Pulse Width                                                   |                                                                                    | 60                            | 200                              | ns(min)                     |

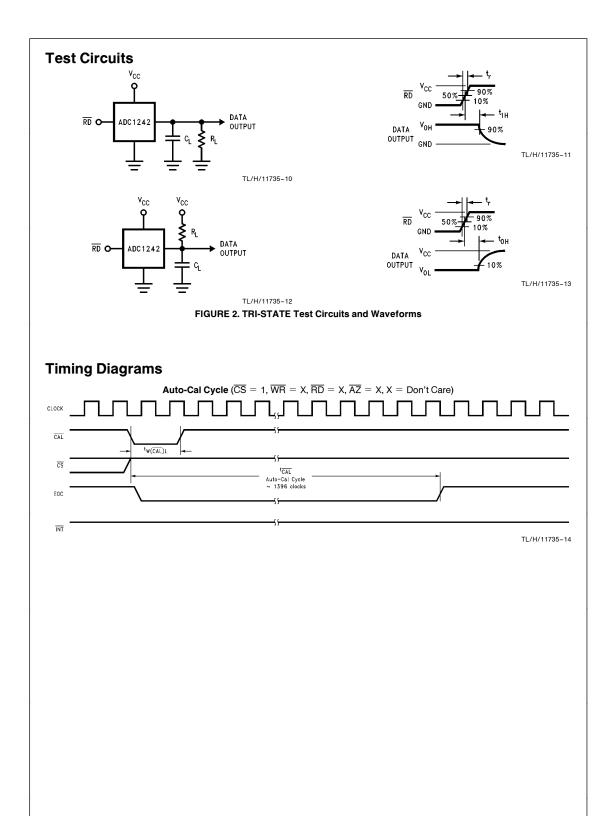

| t <sub>ACC</sub>                  | Maximum Access Time (Delay from Falling Edge of RD to Output Data Valid) | C <sub>L</sub> = 100 pF                                                            | 50                            | 85                               | ns(max)                     |

| t <sub>0H</sub> , t <sub>1H</sub> | TRI-STATE Control (Delay from Rising Edge of RD to Hi-Z State)           | $\begin{aligned} R_L &= 1 \text{ k}\Omega, \\ C_L &= 100 \text{ pF} \end{aligned}$ | 30                            | 90                               | ns(max)                     |

| t <sub>PD(ĪNT)</sub>              | Maximum Delay from Falling Edge of RD or WR to Reset of INT              |                                                                                    | 100                           | 175                              | ns(max)                     |

Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

Note 2: All voltages are measured with respect to AGND and DGND, unless otherwise specified.

Note 3: When the input voltage  $(V_{IN})$  at any pin exceeds the power supply rails  $(V_{IN} < V^- \text{ or } V_{IN}) = (AV_{CC} \text{ or } DV_{CC})$ , the current at that pin should be limited to 5 mA. The 20 mA maximum package input current rating allows the voltage at any four pins, with an input current limit of 5 mA, to simultaneously exceed the power supply voltages.

**Note 4:** The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{JMAX}$  (maximum junction temperature),  $\theta_{JA}$  (package junction to ambient thermal resistance), and  $T_A$  (ambient temperature). The maximum allowable power dissipation at any temperature is  $P_{Dmax} = (T_{Jmax} - T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 125^{\circ}C$ , and the typical thermal resistance  $(\theta_{JA})$  of the ADC1242 CIJ when board mounted is  $47^{\circ}C/W$ .

Note 5: Human body model, 100 pF discharged through a 1.5  $k\Omega$  resistor.

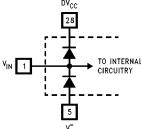

Note 6: Two on-chip diodes are tied to the analog input as shown below. Errors in the A/D conversion can occur if these diodes are forward biased more than 50 mV.

TL/H/11735-

This means that if AV $_{CC}$  and DV $_{CC}$  are minimum (4.75 V $_{DC}$ ) and V $^-$  is maximum (-4.75 V $_{DC}$ ), full-scale must be  $\leq$  4.8 V $_{DC}$ .

### **AC Electrical Characteristics** (Continued)

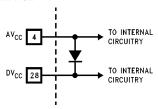

Note 7: A diode exists between AV<sub>CC</sub> and DV<sub>CC</sub> as shown below.

TL/H/11735-4

To guarantee accuracy, it is required that the  $AV_{CC}$  and  $DV_{CC}$  be connected together to a power supply with separate bypass filters at each  $V_{CC}$  pin.

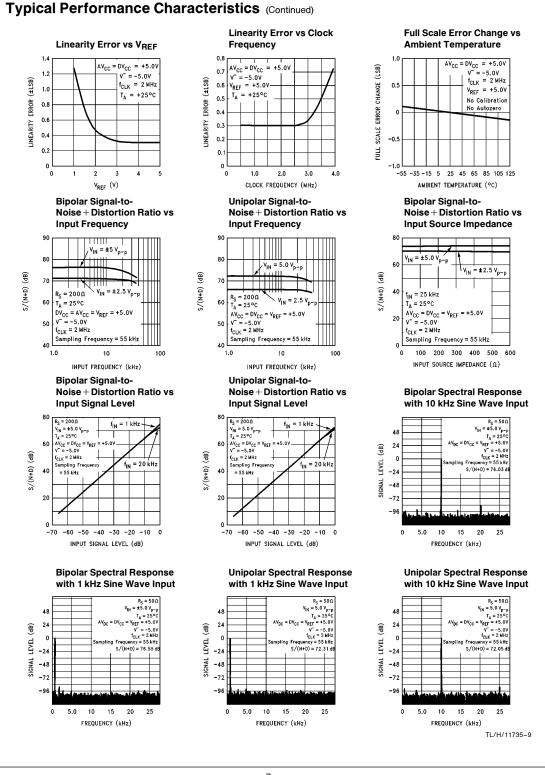

Note 8: Accuracy is guaranteed at f<sub>CLK</sub> = 2.0 MHz. At higher and lower clock frequencies accuracy may degrade. See curves in the Typical Performance Characteristics Section.

Note 9: Typicals are at  $\rm T_{J}\,=\,25^{o}C$  and represent most likely parametric norm.

Note 10: Limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

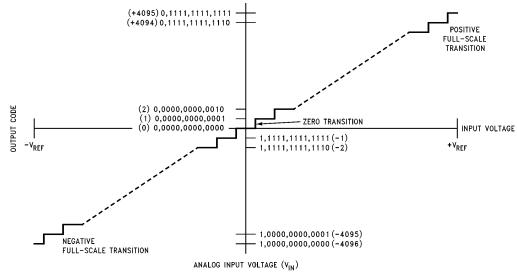

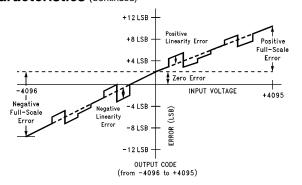

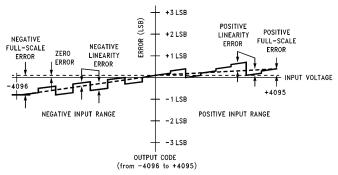

Note 11: Positive linearity error is defined as the deviation of the analog value, expressed in LSBs, from the straight line that passes through positive full scale and zero. For negative linearity error the straight line passes through negative full scale and zero. (See *Figures 1b* and 1c).

Note 12: The ADC1242's self-calibration technique ensures linearity, full scale, and offset errors as specified, but noise inherent in the self-calibration process will result in a repeatability uncertainty of  $\pm 0.20$  LSB.

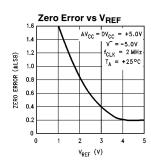

Note 13: If TA changes then an Auto-Zero or Auto-Cal cycle will have to be re-started, see the typical performance characteristic curves.

Note 14: After an Auto-Zero or Auto-Cal cycle at the specified power supply extremes.

Note 15: If the clock is asynchronous to the falling edge of  $\overline{WR}$  an uncertainty of one clock period will exist in the interval of  $t_A$ , therefore making the minimum  $t_A=6$  clock periods and the maximum  $t_A=7$  clock periods. If the falling edge of the clock is synchronous to the rising edge of  $\overline{WR}$  then  $t_A$  will be exactly 6.5 clock periods.

Note 16: The  $\overline{\text{CAL}}$  line must be high before any other conversion is started.

Note 17: The specifications for these parameters are valid after an Auto-Cal cycle has been completed.

Note 18: A military RETS electrical test specification is available upon request. At time of printing, the ADC1241CMJ/883 RETS specification complies fully with the boldface limits in this column.

FIGURE 1a. Transfer Characteristic

TL/H/11735-5

# **AC Electrical Characteristics** (Continued)

FIGURE 1b. Simplified Error Curve vs Output Code without Auto-Cal or Auto-Zero Cycles

FIGURE 1c. Simplified Error Curve vs Output Code after Auto-Cal Cycle

# **Typical Performance Characteristics**

TL/H/11735-8

TL/H/11735-7

TL/H/11735-6

## 1.0 Pin Descriptions

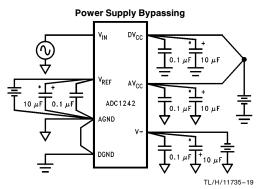

DV<sub>CC</sub> (28), AV<sub>CC</sub> (4) The digital and analog positive power supply pins. The digital and analog power supply voltage range of the ADC1242 is  $\pm 4.5$ V to  $\pm 5.5$ V. To guarantee accuracy, it is required that the AV<sub>CC</sub> and DV<sub>CC</sub> be connected together to the same power supply with separate bypass filters (10  $\mu$ F tantalum in parallel

V $^-$ (5) The analog negative supply voltage pin. V $^-$ has a range of -4.5V to -5.5V and needs a bypass filter of 10  $\mu$ F tantalum in parallel with a 0.1  $\mu$ F ceramic.

with a 0.1  $\mu$ F ceramic) at each V<sub>CC</sub> pin.

DGND (14), The digital and analog ground pins. AGND AGND (3) and DGND must be connected together externally to guarantee accuracy.

V<sub>REF</sub> (2) The reference input voltage pin. To maintain accuracy the voltage at this pin should not exceed the AV<sub>CC</sub> or DV<sub>CC</sub> by more than 50 mV or go below 3.5 VDC.

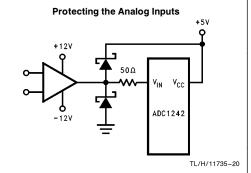

V<sub>IN</sub> (1) The analog input voltage pin. To guarantee accuracy the voltage at this pin should not exceed V<sub>CC</sub> by more than 50 mV or go below V<sup>-</sup> by more than 50 mV.

CS (10) The Chip Select control input. This input is active low and enables the WR and RD functions

RD (11) The Read control input. With both  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  low the TRI-STATE output buffers are enabled and the  $\overline{\text{INT}}$  output is reset high.

$\overline{WR}$  (7) The Write control input. The converison is started on the rising edge of the  $\overline{WR}$  pulse when  $\overline{CS}$  is low.

CLK (8) The external clock input pin. The clock frequency range is 500 kHz to 4 MHz.

The Auto-Calibration control input. When CAL is low the ADC1242 is reset and a calibration cycle is initiated. During the calibration cycle the values of the comparator offset voltage and the mismatch errors in the capacitor reference ladder are determined and stored in RAM. These values are used to correct the errors during a normal cycle of A/D conversion

\$\overline{AZ}\$ (6) The Auto-Zero control input. With the \$\overline{AZ}\$ pin held low during a conversion, the ADC1242 goes into an auto-zero cycle before the actual A/D conversion is started. This Auto-Zero cycle corrects for the comparator offset voltage. The total conversion time (t<sub>C</sub>) is increased by 26 clock periods when Auto-Zero is used.

EOC (12) The End-of-Conversion control output. This output is low during a conversion or a calibration cycle.

INT (13) The Interrupt control output. This output goes low when a conversion has been completed and indicates that the conversion result is available in the output latches. Reading the result or starting a conversion or calibration cycle will reset this output high.

DB0-DB12 The TRI-STATE output pins. The output is in two's complement format with DB12 the sign bit, DB11 the MSB and DB0 the LSB.

## 2.0 Functional Description

The ADC1242 is a 12-bit plus sign A/D converter with the capability of doing Auto-Zero or Auto-Cal routines to minimize zero, full-scale and linearity errors. It is a successive-approximation A/D converter consisting of a DAC, comparator and a successive-approximation register (SAR). Auto-Zero is an internal calibration sequence that corrects for the A/D's zero error caused by the comparator's offset voltage. Auto-Cal is a calibration cycle that not only corrects zero error but also corrects for full-scale and linearity errors caused by DAC inaccuracies. Auto-Cal minimizes the errors of the ADC1242 without the need of trimming during its fabrication. An Auto-Cal cycle can restore the accuracy of the ADC1242 at any time, which ensures its long term stability.

#### 2.1 DIGITAL INTERFACE

On power up, a calibration sequence should be initiated by pulsing  $\overline{CAL}$  low with  $\overline{CS}$ ,  $\overline{RD}$ , and  $\overline{WR}$  high. To acknowledge the  $\overline{CAL}$  signal, EOC goes low after the falling edge of  $\overline{CAL}$ , and remains low during the calibration cycle of 1396 clock periods. During the calibration sequence, first the comparator's offset is determined, then the capacitive DAC's mismatch error is found. Correction factors for these errors are then stored in internal RAM.

A conversion is initiated by taking  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  low. The  $\overline{\text{AZ}}$  (Auto Zero) signal line should be tied high or low during the conversion process. If  $\overline{\text{AZ}}$  is low an auto zero cycle, which takes approximately 26 clock periods, occurs before the actual conversion is started. The auto zero cycle determines the correction factors for the comparator's offset voltage. If  $\overline{\text{AZ}}$  is high, the auto zero cycle is skipped. Next the analog input is sampled for 7 clock periods, and held in the capacitive DAC's ladder structure. The EOC then goes low, signaling that the analog input is no longer being sampled and that the A/D successive approximation conversion has started

During a conversion, the sampled input voltage is successively compared to the output of the DAC. First, the acquired input voltage is compared to analog ground to determine its polarity. The sign bit is set low for positive input voltages and high for negative. Next the MSB of the DAC is set high with the rest of the bits low. If the input voltage is greater than the output of the DAC, then the MSB is left high; otherwise it is set low. The next bit is set high, making the output of the DAC three guarters or one guarter of full scale. A comparison is done and if the input is greater than the new DAC value this bit remains high; if the input is less than the new DAC value the bit is set low. This process continues until each bit has been tested. The result is then stored in the output latch of the ADC1242. Next EOC goes high, and  $\overline{\mbox{INT}}$  goes low to signal the end of the conversion. The result can now be read by taking  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  low to enable the DB0-DB12 output buffers.

# 2.0 Functional Description (Continued)

| Digital Control Inputs |    |    |     | 5  | A/D Function                                    |  |

|------------------------|----|----|-----|----|-------------------------------------------------|--|

| CS                     | WR | RD | CAL | ĀΖ | A, b 1 unction                                  |  |

| T                      | T  | 1  | 1   | 1  | Start Conversion without Auto-Zero              |  |

| T                      | 1  | Т  | 1   | 1  | Read Conversion Result without Auto-Zero        |  |

| 고                      | ᇺ  | 1  | 1   | 0  | Start Conversion with Auto-Zero                 |  |

| T                      | 1  | Т  | 1   | 0  | Read Conversion Result with Auto-Zero           |  |

| 1                      | Х  | Χ  | Ţ   | Х  | Start Calibration Cycle                         |  |

| 0                      | Х  | 1  | 0   | Х  | Test Mode (DB2, DB3, DB5 and DB6 become active) |  |

FIGURE 3. Function of the A/D Control Inputs

The table in Figure 3 summarizes the effect of the digital control inputs on the function of the ADC1242. The Test Mode, where  $\overline{\text{RD}}$  is high and  $\overline{\text{CS}}$  and  $\overline{\text{CAL}}$  are low, is used by the factory to thoroughly check out the operation of the ADC1242. Care should be taken not to inadvertently be in this mode, since DB2, DB3, DB5, and DB6 become active outputs, which may cause data bus contention.

#### 2.2 RESETTING THE A/D

All internal logic can be reset, which will abort any conversion in process. The A/D is reset whenever a new conversion is started by taking  $\overline{\text{CS}}$  and  $\overline{\text{WR}}$  low. If this is done when the analog input is being sampled or when EOC is low, the Auto-Cal correction factors may be corrupted, therefore making it necessary to do an Auto-Cal cycle before the next conversion. This is true with or without Auto-Zero. The Calibration Cycle cannot be reset once started. On power-up the ADC1242 automatically goes through a Calibration Cycle that takes typically 1396 clock cycles.

# 3.0 Analog Considerations

### 3.1 REFERENCE VOLTAGE

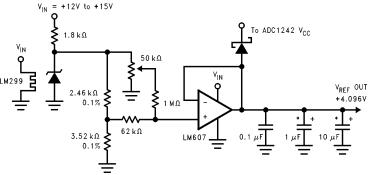

The voltage applied to the reference input of the converter defines the voltage span of the analog input (the difference between  $V_{\rm IN}$  and AGND), over which 4095 positive output codes and 4096 negative output codes exist. The A-to-D can be used in either ratiometric or absolute reference applications. The voltage source driving  $V_{\rm REF}$  must have a very low output impedance and very low noise. The circuit in Figure 4 is an example of a very stable reference that is appropriate for use with the ADC1242.

In a ratiometric system, the analog input voltage is proportional to the voltage used for the A/D reference. When this voltage is the system power supply, the  $V_{\rm REF}$  pin can be tied to  $V_{\rm CC}.$  This technique relaxes the stability requirement of the system reference as the analog input and A/D reference move together maintaining the same output code for given input condition.

\*Tantalum

TL/H/11735-17

FIGURE 4. Low Drift Extremely Stable Reference Circuit

# 3.0 Analog Considerations (Continued)

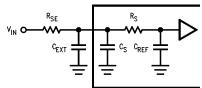

FIGURE 5. Analog Input Equivalent Circuit

TL/H/11735-18

For absolute accuracy, where the analog input varies between very specific voltage limits, the reference pin can be biased with a time and temperature stable voltage source. In general, the magnitude of the reference voltage will require an initial adjustment to null out full-scale errors.

#### **3.2 INPUT CURRENT**

A charging current will flow into or out of (depending on the input voltage polarity) of the analog input pin  $(V_{IN})$  on the start of the analog input sampling period  $(t_A)$ . The peak value of this current will depend on the actual input voltage applied.

### 3.3 INPUT BYPASS CAPACITORS

An external capacitor can be used to filter out any noise due to inductive pickup by a long input lead and will not degrade the accuracy of the conversion result.

#### 3.4 INPUT SOURCE RESISTANCE

The analog input can be modeled as shown in Figure 5. External  $R_{SE}$  will lengthen the time period necessary for the voltage on  $C_{REF}$  to settle to within  $^{1}\!/_{2}$  LSB of the analog input voltage. With  $f_{CLK}=2$  MHz  $t_{A}=7$  clock periods = 3.5  $\mu_{S}$ ,  $R_{SE}\leq 1$  k $\Omega$  will allow a 5V analog input voltage to settle properly.

### 3.5 NOISE

The leads to the analog input pin should be kept as short as possible to minimize input noise coupling. Both noise and undesired digital clock coupling to this input can cause errors. Input filtering can be used to reduce the effects of these noise sources.

#### 3.6 POWER SUPPLIES

Noise spikes on the  $V_{CC}$  and  $V^-$  supply lines can cause conversion errors as the comparator will respond to this noise. The A/D is especially sensitive during the auto-zero or auto-cal procedures to any power supply spikes. Low in

ductance tantalum capacitors of 10  $\mu F$  or greater paralleled with 0.1  $\mu F$  ceramic capacitors are recommended for supply bypassing. Separate bypass capacitors whould be placed close to the DV<sub>CC</sub>, AV<sub>CC</sub> and V $^-$  pins. If an unregulated voltage source is available in the system, a separate LM340LAZ-5.0 voltage regulator for the A-to-D's V<sub>CC</sub> (and other analog circuitry) will greatly reduce digital noise on the supply line.

### 3.7 THE CALIBRATION CYCLE

On power up the ADC1242 goes through an Auto-Cal cycle which cannot be interrupted. Since the power supply, reference, and clock will not be stable at power up, this first calibration cycle will not result in an accurate calibration of the A/D. A new calibration cycle needs to be started after the power supplies, reference, and clock have been given enough time to stabilize. During the calibration cycle, correction values are determined for the offset voltage of the sampled data comparator and any linearity and gain errors. These values are stored in internal RAM and used during an analog-to-digital conversion to bring the overall gain, offset, and linearity errors down to the specified limits. It should be necessary to go through the calibration cycle only once after power up.

#### 3.8 THE AUTO-ZERO CYCLE

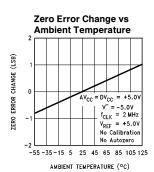

To correct for any change in the zero (offset) error of the A/D, the auto-zero cycle can be used. It may be necessary to do an auto-zero cycle whenever the ambient temperature changes significantly. (See the curved titled "Zero Error Change vs Ambient Temperature" in the Typical Performance Characteristics.) A change in the ambient temperature will cause the  $V_{OS}$  of the sampled data comparator to change, which may cause the zero error of the A/D to be greater than the amount specified. An auto-zero cycle will maintain the zero error to the amount specified or less.

# 4.0 Dynamic Performance

Many applications require the A/D converter to digitize ac signals, but the standard dc integral and differential nonlinearity specifications will not accurately predict the A/D converter's performance with ac input signals. The important specifications for ac applications reflect the converter's ability to digitize ac signals without significant spectral errors and without adding noise to the digitized signal. Dynamic characteristics such as signal-to-noise+distortion ratio (S/(N+D)), effective bits, full power bandwidth, aperture time and aperture jitter are quantitative measures of the A/D converter's capability.

An A/D converter's ac performance can be measured using Fast Fourier Transform (FFT) methods. A sinusoidal waveform is applied to the A/D converter's input, and the transform is then performed on the digitized waveform. S/(N+D) is calculated from the resulting FFT data, and a spectral plot may also be obtained. Typical values for S/(N+D) are shown in the table of Electrical Characteristics, and spectral plots are included in the typical performance curves.

The A/D converter's noise and distortion levels will change with the frequency of the input signal, with more distortion and noise occurring at higher signal frequencies. This can be seen in the S/(N+D) versus frequency curves. These curves will also give an indication of the full power bandwidth (the frequency at which the S/(N+D) drops 3 dB).

Two sample/hold specifications, aperture time and aperture jitter, are included in the Dynamic Characteristics table since the ADC1242 has the ability to track and hold the analog input voltage. Aperture time is the delay for the A/D to respond to the hold command. In the case of the ADC1242, the hold command is internally generated. When the Auto-Zero function is not being used, the hold command occurs at the end of the acquisition window, or seven clock periods after the rising edge of the WR. The delay between the internally generated hold command and the time that the ADC1242 actually holds the input signal is the aperture time. For the ADC1242, this time is typically 100 ns. Aperture jitter is the change in the aperture time from sample to sample. Aperture jitter is useful in determining the maximum slew rate of the input signal for a given accuracy. For example, an ADC1242 with 100 ps of aperture jitter operating with a 5V reference can have an effective gain variation of about 1 LSB with an input signal whose slew rate is 12  $V/\mu s$ .

\*Tantalum

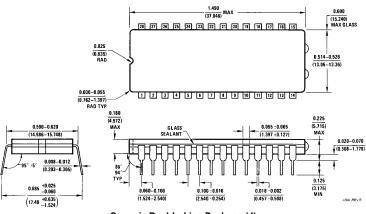

# Physical Dimensions inches (millimeters)

Ceramic Dual-In-Line Package (J) Order Number ADC1242CIJ NS Package Number J28A

### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

National Semiconductor Corporation 1111 West Bardin Road Arlington, TX 76017 Tel: 1(800) 272-9959 Fax: 1(800) 737-7018 National Semiconductor Europe

Fax: (+49) 0-180-530 85 86 Email: cnjwge@tevm2.nsc.com Deutsch Tel: (+49) 0-180-530 85 85 English Tel: (+49) 0-180-532 78 32 Français Tel: (+49) 0-180-532 93 58 Italiano Tel: (+49) 0-180-534 16 80 National Semiconductor Hong Kong Ltd. 13th Floor, Straight Block, Ocean Centre, 5 Canton Rd. Tsimshatsui, Kowloon Hong Kong Tel: (852) 2737-1600 Fax: (852) 2736-9960 National Semiconductor Japan Ltd. Tel: 81-043-299-2309 Fax: 81-043-299-2408