SNLS174D - APRIL 2005 - REVISED SEPTEMBER 2011

# CLC034 SMPTE 292M / 259M Adaptive Cable Equalizer

Check for Samples: CLC034

## **FEATURES**

- SMPTE 292M, SMPTE 344M and SMPTE 259M Compliant

- Supports DVB-ASI at 270 Mbps

- High Data Rates: 143 Mbps to 1.485 Gbps

- Equalizes up to 140 Meters of Belden 1694A at 1.485 Gbps or up to 350 Meters of Belden 1694A at 270 Mbps

- Manual Bypass, Cable Length Indicator, and **Output Mute with a Programmable Threshold**

- Single-Ended or Differential Input

- 50Ω Differential Outputs

- Single 3.3V Supply Operation

- 208mW Typical Power Consumption with 3.3V Supply

- Replaces the GS1524 and GS1524A

## **APPLICATIONS**

- SMPTE 292M, SMPTE 344M, and SMPTE 259M **Serial Digital Interfaces**

- **Serial Digital Data Equalization and Reception**

- **Data Recovery Equalization**

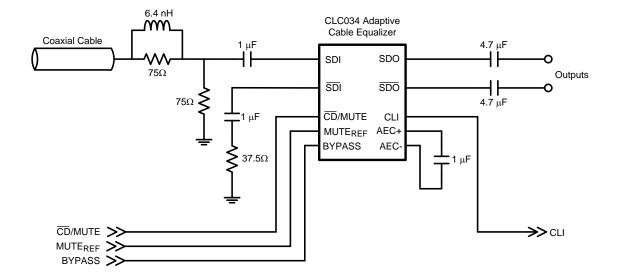

## TYPICAL APPLICATION

## **DESCRIPTION**

The CLC034 SMPTE 292M / 259M adaptive cable equalizer is a monolithic integrated circuit for equalizing data transmitted over cable (or any media with similar dispersive loss characteristics). The equalizer operates over a wide range of data rates from 143 Mbps to 1.485 Gbps and supports SMPTE 292M, SMPTE 344M and SMPTE 259M.

The CLC034 implements DC restoration to correctly handle pathological data conditions. DC restoration can be bypassed for low data rate applications. The equalizer is flexible in allowing either single-ended or differential input drive.

Additional features include a combined carrier detect and output mute pin which mutes the output when no signal is present. A programmable mute reference is used to mute the output at a selectable level of signal degradation. A cable length indicator is provided to determine the amount of cable being equalized.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

All trademarks are the property of their respective owners.

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

## ABSOLUTE MAXIMUM RATINGS (1)

|                                    | . • •                       |                                |  |  |

|------------------------------------|-----------------------------|--------------------------------|--|--|

| Supply Voltage                     | -0.5V to 3.6V               |                                |  |  |

| Input Voltage (all inputs)         |                             | -0.3V to V <sub>CC</sub> +0.3V |  |  |

| Storage Temperature Range          |                             | −65°C to +150°C                |  |  |

| Junction Temperature               |                             | +150°C                         |  |  |

| Lead Temperature (Soldering 4 Sec) |                             | +260°C                         |  |  |

| Package Thermal Resistance         | θ <sub>JA</sub> 16-pin SOIC | +115°C/W                       |  |  |

|                                    | θ <sub>JC</sub> 16-pin SOIC | +105°C/W                       |  |  |

| ESD Rating (HBM)                   |                             | 8kV                            |  |  |

| ESD Rating (MM)                    | 250V                        |                                |  |  |

<sup>(1) &</sup>quot;Absolute Maximum Ratings" are those parameter values beyond which the life and operation of the device cannot be guaranteed. The stating herein of these maximums shall not be construed to imply that the device can or should be operated at or beyond these values. The table of "Electrical Characteristics" specifies acceptable device operating conditions.

#### RECOMMENDED OPERATING CONDITIONS

| Supply Voltage (V <sub>CC</sub> – V <sub>EE</sub> ) | 3.3V ±5%     |

|-----------------------------------------------------|--------------|

| Input Coupling Capacitance                          | 1.0 µF       |

| AEC Capacitor (Connected between AEC+ and AEC-)     | 1.0 µF       |

| Operating Free Air Temperature (T <sub>A</sub> )    | 0°C to +85°C |

#### DC ELECTRICAL CHARACTERISTICS

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1)(2).

| Symbol             | Parameter                                 | Conditions                                                                                                | Reference           | Min | Тур                                      | Max | Units             |

|--------------------|-------------------------------------------|-----------------------------------------------------------------------------------------------------------|---------------------|-----|------------------------------------------|-----|-------------------|

| $V_{CMIN}$         | Input Common Mode Voltage                 |                                                                                                           | SDI, SDI            |     | 1.9                                      |     | V                 |

| V <sub>SDI</sub>   | Input Voltage Swing                       | At CLC034 input, 1.485 Gbps, $T_A$ = +25°C to +85°C, $\overline{CD}$ /MUTE may be used, $^{(3)}$ (4)      |                     | 720 | 800                                      | 880 | mV <sub>P-P</sub> |

|                    |                                           | At CLC034 input, 270 Mbps, $T_A$ = +25°C to +85°C, $\overline{CD}/MUTE$ may be used, $^{(3)}$ $^{(4)}(5)$ |                     | 720 | 800                                      | 830 | mV <sub>P-P</sub> |

|                    |                                           | At CLC034 input, 143 to 1485<br>Mbps, CD/MUTE tied to GND<br>(MUTE disabled), (3)(4)(5)                   |                     | 720 | 800                                      | 950 | mV <sub>P-P</sub> |

| V <sub>CMOUT</sub> | Output Common Mode Voltage                |                                                                                                           | SDO, SDO            |     | V <sub>CC</sub> –<br>V <sub>SDO</sub> /2 |     | V                 |

| $V_{SDO}$          | Output Voltage Swing                      | 50Ω load, differential                                                                                    |                     |     | 750                                      |     | $mV_{P-P}$        |

|                    | CLI DC Voltage                            | 0m cable                                                                                                  | CLI                 |     | 2.5                                      |     | V                 |

|                    |                                           | no signal                                                                                                 |                     |     | 1.2                                      |     | V                 |

|                    | MUTE <sub>REF</sub> DC Voltage (floating) |                                                                                                           | MUTE <sub>REF</sub> |     | 1.3                                      |     | V                 |

|                    | MUTE <sub>REF</sub> Range                 |                                                                                                           |                     |     | 0.7                                      |     | V                 |

Product Folder Links: CLC034

<sup>(1)</sup> Current flow into device pins is defined as positive. Current flow out of device pins is defined as negative. All voltages are stated referenced to  $V_{EE} = 0$  Volts.

Typical values are stated for  $V_{CC}$  = +3.3V and  $T_A$  = +25°C.

Specification is ensured by characterization.

The maximum input voltage swing assumes a nonstressing, DC-balance signal; specifically, the SMPTE-recommended color bar test signal. Pathological or other stressing signals may not be used. This specification is for 0m cable only.

The CLC034 is fully compatible with the 800mV<sub>P.P</sub> ±10% SMPTE 259M generator specification when CD/MUTE is tied to GND (MUTE is disabled). For 143 Mpbs input, CD/MUTE should always be tied to GND.

## DC ELECTRICAL CHARACTERISTICs (continued)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1)(2).

| Symbol          | Parameter              | Conditions                  | Reference | Min | Тур | Max | Units |

|-----------------|------------------------|-----------------------------|-----------|-----|-----|-----|-------|

|                 | CD/MUTE Output Voltage | Carrier not present         | CD/MUTE   | 2.6 |     |     | V     |

|                 |                        | Carrier present             |           |     |     | 0.4 | V     |

|                 | CD/MUTE Input Voltage  | Min to mute outputs         |           | 3.0 |     |     | V     |

|                 |                        | Max to force outputs active |           |     |     | 2.0 | V     |

| I <sub>CC</sub> | Supply Current         | See (6)                     |           |     | 63  | 77  | mA    |

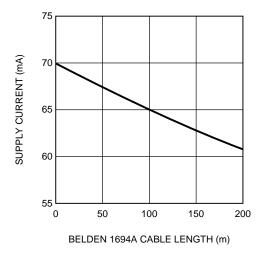

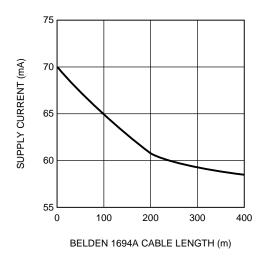

Supply current depends on the amount of cable being equalized. The current is highest for short cable and decreases as the cable length is increased. Refer to Figure 2 and Figure 3.

#### **AC ELECTRICAL CHARACTERISTICS**

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified (1).

| Symbol                         | Parameter                                                          | Conditions                                                       | Reference | Min | Тур   | Max  | Units |

|--------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------|-----------|-----|-------|------|-------|

| BR <sub>SDI</sub>              | Input Data Rate                                                    |                                                                  | SDI, SDI  | 143 |       | 1485 | Mbps  |

|                                | Maximum Equalized Cable<br>Length (with equalizer<br>pathological) | 270 Mbps, Belden 1694A,<br>0.2UI output jitter, <sup>(2)</sup>   |           |     | 350   |      | m     |

|                                |                                                                    | 270 Mbps, Belden 8281, 0.2UI output jitter, (2)                  |           |     | 280   |      | m     |

|                                |                                                                    | 1.485 Gbps, Belden 1694A, 0.25UI output jitter, <sup>(2)</sup>   |           |     | 140   |      | m     |

|                                |                                                                    | 1.485 Gbps, Belden 8281,<br>0.25UI output jitter, <sup>(2)</sup> |           |     | 100   |      | m     |

| t <sub>r</sub> ,t <sub>f</sub> | Output Rise Time, Fall Time                                        | 20% – 80%, (2)                                                   | SDO, SDO  |     | 100   | 220  | ps    |

|                                | Mismatch in Rise/Fall Time                                         | (2)                                                              |           |     | 2     | 15   | ps    |

| tos                            | Output Overshoot                                                   | (2)                                                              |           |     | 1     | 5    | %     |

| R <sub>OUT</sub>               | Output Resistance                                                  | single-ended, (3)                                                |           |     | 50    |      | Ω     |

| RL <sub>IN</sub>               | Input Return Loss                                                  | See (4)                                                          | SDI, SDI  | 15  | 18-20 |      | dB    |

| R <sub>IN</sub>                | Input Resistance                                                   | single-ended                                                     |           |     | 1.3   |      | kΩ    |

| C <sub>IN</sub>                | Input Capacitance                                                  | single-ended, (3)                                                |           |     | 1     |      | pF    |

- (1) Typical values are stated for  $V_{CC}$  = +3.3V and  $T_A$  = +25°C. (2) Specification is ensured by characterization.

- Specification is ensured by design.

- Input return loss is dependent on board design. The CLC034 meets this specification on the SD034 evaluation board from 5MHz to 1.5GHz.

## **CONNECTION DIAGRAM**

Figure 1. 16-Pin SOIC See Package Number D0016A

Product Folder Links: CLC034

Copyright © 2005-2011, Texas Instruments Incorporated

## **PIN DESCRIPTIONS**

| Pin # | Name                | Description                                                                                                                                                                                                                                                                                                                         |

|-------|---------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | CLI                 | Cable length indicator. Provides a voltage inversely proportional to the cable length being equalized.                                                                                                                                                                                                                              |

| 2     | V <sub>CC</sub>     | Positive power supply (+3.3V).                                                                                                                                                                                                                                                                                                      |

| 3     | V <sub>EE</sub>     | Negative power supply (ground).                                                                                                                                                                                                                                                                                                     |

| 4     | SDI                 | Serial data true input.                                                                                                                                                                                                                                                                                                             |

| 5     | SDI                 | Serial data complement input.                                                                                                                                                                                                                                                                                                       |

| 6     | V <sub>EE</sub>     | Negative power supply (ground).                                                                                                                                                                                                                                                                                                     |

| 7     | AEC+                | AEC loop filter external capacitor (1μF) positive connection.                                                                                                                                                                                                                                                                       |

| 8     | AEC-                | AEC loop filter external capacitor (1μF) negative connection.                                                                                                                                                                                                                                                                       |

| 9     | BYPASS              | Bypasses equalization and DC restoration when high. No equalization occurs in this mode.                                                                                                                                                                                                                                            |

| 10    | MUTE <sub>REF</sub> | Mute reference. Determines the maximum cable to be equalized before muting. May be unconnected for maximum equalization.                                                                                                                                                                                                            |

| 11    | V <sub>EE</sub>     | Negative power supply (ground).                                                                                                                                                                                                                                                                                                     |

| 12    | SDO                 | Serial data complement output.                                                                                                                                                                                                                                                                                                      |

| 13    | SDO                 | Serial data true output.                                                                                                                                                                                                                                                                                                            |

| 14    | V <sub>EE</sub>     | Negative power supply (ground).                                                                                                                                                                                                                                                                                                     |

| 15    | V <sub>CC</sub>     | Positive power supply (+3.3V).                                                                                                                                                                                                                                                                                                      |

| 16    | CD/MUTE             | Bi-directional carrier detect and output mute. $\overline{\text{CD}}/\text{MUTE}$ is high when no signal is present. If unconnected, MUTE is controlled automatically by carrier detect. To force MUTE on, tie to V <sub>CC</sub> . To disable MUTE, tie to GND. $\overline{\text{CD}}/\text{MUTE}$ has no function in BYPASS mode. |

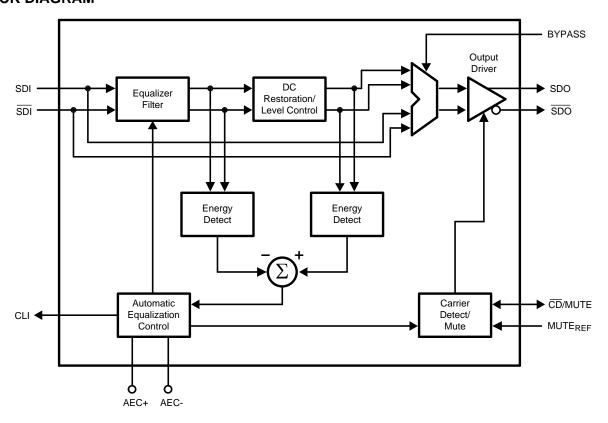

## **BLOCK DIAGRAM**

Submit Documentation Feedback

Copyright © 2005–2011, Texas Instruments Incorporated

SNLS174D - APRIL 2005 - REVISED SEPTEMBER 2011

#### **DEVICE OPERATION**

#### **BLOCK DESCRIPTION**

The **Equalizer Filter** block is a multi-stage adaptive filter. If Bypass is high, the equalizer filter is disabled.

The **DC Restoration / Level Control** block receives the differential signals from the equalizer filter block. This block incorporates a self-biasing DC restoration circuit to fully DC restore the signals. If Bypass is high, this function is disabled.

The signals before and after the DC Restoration / Level Control block are used to generate the **Automatic Equalization Control (AEC)** signal. This control signal sets the gain and bandwidth of the equalizer filter. The loop response in the AEC block is controlled by an external 1µF capacitor placed across the AEC+ and AEC-pins. **Cable Length Indicator (CLI)** is derived from this block.

The Carrier Detect / Mute block generates the carrier detect signal and controls the mute function of the output. This block utilizes the bi-directional CD/MUTE signal along with Mute Reference (MUTE<sub>REF</sub>).

The **Output Driver** produces SDO and SDO.

## **CABLE LENGTH INDICATOR (CLI)**

The cable length indicator provides a voltage to indicate the length of cable being equalized. The CLI voltage decreases as the cable length increases.

## MUTE REFERENCE (MUTE<sub>REF</sub>)

The mute reference determines the amount of cable to equalize before automatically muting the outputs. This is set by applying a voltage inversely proportional to the length of cable to equalize. As the applied MUTE<sub>REF</sub> voltage is increased, the amount of cable that can be equalized before carrier detect is de-asserted and the outputs are muted is decreased. MUTE<sub>REF</sub> may be left unconnected for maximum equalization before muting.

## CARRIER DETECT / MUTE (CD/MUTE)

Carrier Detect / Mute is bi-directional, serving as both a carrier detect (output function) and mute (input function).

When used as an output,  $\overline{\text{CD}}/\text{MUTE}$  determines if a valid signal is present at the CLC034 input. If MUTE<sub>REF</sub> is used, the carrier detect threshold will be altered accordingly.  $\overline{\text{CD}}/\text{MUTE}$  provides a high voltage when no signal is present at the CLC034 input, and the outputs are automatically muted. This is true if no cable is connected to the input or if the input cable is very long, typically 450m Belden 1694A for 1.485 Gbps input or 550m Belden 1694A for 270 Mbps input (with standard 800 mV<sub>P-P</sub> color bar input signals).  $\overline{\text{CD}}/\text{MUTE}$  is low when a valid input signal has been detected, and the outputs are automatically enabled.

As an input,  $\overline{\text{CD}}/\text{MUTE}$  can be used to override the carrier detect and manually mute or enable the CLC034 outputs. Applying a high input to  $\overline{\text{CD}}/\text{MUTE}$  will mute the CLC034 outputs. Applying a low input will force the outputs to be active regardless of the length of cable or the state of MUTE<sub>RFF</sub>.

#### INPUT INTERFACING

The CLC034 accepts either differential or single-ended input. The input must be AC coupled. Transformer coupling is not supported.

The CLC034 correctly handles equalizer pathological signals for standard definition and high definition serial digital video, as described in SMPTE RP 178 and RP 198, respectively.

## **OUTPUT INTERFACING**

The SDO and  $\overline{\text{SDO}}$  outputs are internally loaded with 50 $\Omega$ . They produce a 750 mV<sub>P-P</sub> differential output, or a 375 mV<sub>P-P</sub> single-ended output.

Product Folder Links: CLC034

#### **APPLICATION INFORMATION**

#### PCB LAYOUT RECOMMENDATIONS

Please refer to the following Application Note on Texas Instruments' website: AN-1372, "CLC034 PCB Layout Techniques."

#### **REPLACING THE GENNUM GS1524**

The CLC034 is footprint compatible with the Gennum GS1524 and GS1524A.

#### SUPPLY CURRENT VS. CABLE LENGTH

The supply current ( $I_{CC}$ ) depends on the amount of cable being equalized. The current is highest for short cable and decreases as the cable length is increased. Figure 2 shows supply current vs. Belden 1694A cable length for 1.485 Gbps data and Figure 3 shows supply current vs. Belden 1694A cable length for 270 Mbps data.

Figure 2. Supply Current vs. Belden 1694A Cable Length, 1.485 Gbps

Figure 3. Supply Current vs. Belden 1694A Cable Length, 270 Mbps

#### ADDITIONAL DETAILS FOR USING CARRIER DETECT / MUTE FEATURE

Table 1 outlines the equalizer input operating conditions based on zero meters of cable length. This is not a condition normally seen in standard applications of SDI equalizers. Typically there is some length of cable between the signal source and the equalizer (hence the need for equalization). Any cable length will attenuate (reduce) the SDI signal amplitude from the amplitude transmitted at the source. The table specifies voltage levels measured at the input of the equalizer which is equivalent to a zero meter cable length from the signal source.

<u>The</u> output will mute if the SDI input signal ( $V_{SDI}$ ) exceeds the maximum input voltage ( $V_{SDI}$  max). Disable CD/MUTE (tie it to GND) to avoid unwanted muting of the output.

Submit Documentation Feedback

SNLS174D - APRIL 2005-REVISED SEPTEMBER 2011

# Table 1. $V_{SDI}$ Conditions for Proper $\overline{CD}/MUTE$ Use vs. Input Data Rate

| Input Data Rate (Mbps) | Conditions if CD/MUTE Used                                                | Conditions if CD/MUTE Disabled(CD/MUTE Tied to GND)                               |

|------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------------------------------|

| 143, 177               | Do not use CD/MUTE (tie it to GND)                                        |                                                                                   |

| 270, 360, 540          | Acceptable V <sub>SDI</sub> : 720 to 830 mV <sub>P-P</sub> <sup>(1)</sup> | Acceptable V <sub>SDI</sub> : 720 to 950 mV <sub>P-P</sub> (all input data rates) |

| 1485                   | Acceptable V <sub>SDI</sub> : 720 to 880 mV <sub>P-P</sub>                |                                                                                   |

<sup>(1)</sup> For 270 Mbps input data rates, the CLC034's maximum acceptable  $V_{SDI}$  is only 0.5 dB below the SMPTE 259M specified 880 m $V_{P-P}$  amplitude for zero meters cable. A 10m length of Belden 8281 cable attenuates the signal enough for SMPTE 259M compliance.

Product Folder Links: CLC034

#### IMPORTANT NOTICE

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have not been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

#### **Products Applications**

power.ti.com

Audio www.ti.com/audio Automotive and Transportation www.ti.com/automotive Communications and Telecom **Amplifiers** amplifier.ti.com www.ti.com/communications **Data Converters** dataconverter.ti.com Computers and Peripherals www.ti.com/computers **DLP® Products** www.dlp.com Consumer Electronics www.ti.com/consumer-apps

DSP **Energy and Lighting** dsp.ti.com www.ti.com/energy Clocks and Timers www.ti.com/clocks Industrial www.ti.com/industrial Interface interface.ti.com Medical www.ti.com/medical logic.ti.com Logic Security www.ti.com/security Space, Avionics and Defense www.ti.com/space-avionics-defense

Microcontrollers microcontroller.ti.com Video and Imaging www.ti.com/video

**RFID** www.ti-rfid.com

Power Mgmt

**OMAP Applications Processors** www.ti.com/omap **TI E2E Community** e2e.ti.com

Wireless Connectivity www.ti.com/wirelessconnectivity