# QUADRUPLE D-TYPE | \$54175 EDGE-TRIGGERED FLIP-FLOPS

N74175

\$54175-B.F.W • N74175-B.F

# DIGITAL 54/74 TTL SERIES

#### DESCRIPTION

These monolithic, positive-edge-triggered flip-flops utilize TTL circuits to implement the D-type flip-flop logic. Information at input D is transferred to the Q output on the positive-going edge of the clock pulse. Clock triggering occurs at a voltage level of the clock pulse and is not directly related to the transition time of the positive-going pulse. When the clock input is at either the high or low level, the D-input signal has no effect.

These circuits are fully compatible for use with most TTL or DTL circuits. A full fan-out to 10 low logic-level loads and 20 highlogic-level loads is available from each of the outputs. This simplifies system design by allowing unused inputs to be tied to driven inputs. Maximum clock frequency is typically 25 megahertz, with a typical power dissipation of 38 milliwatts per flip-flop.

#### TRUTH TABLE

| INPUT          | OUTPUT             |

|----------------|--------------------|

| t <sub>n</sub> | t <sub>n</sub> + 1 |

| D              | a                  |

| н              | н                  |

| L              | L                  |

tn = Bit time before clock pulse transition.  $t_n + 1 = Bit$  time after clock pulse transition.

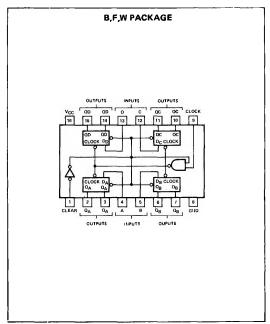

### PIN CONFIGURATION

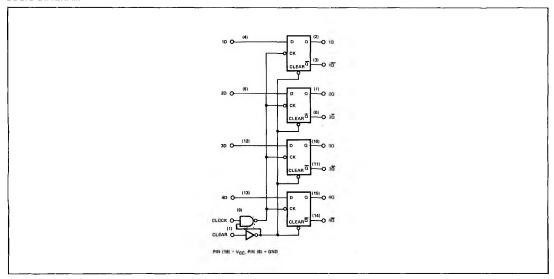

#### LOGIC DIAGRAM

## RECOMMENDED OPERATING CONDITIONS

|                                                            |                     | 54175 |     |     | 74175 |     |      |      |

|------------------------------------------------------------|---------------------|-------|-----|-----|-------|-----|------|------|

|                                                            |                     | MIN   | NOM | MAX | MIN   | NOM | MAX  | UNIT |

| Supply voltage, V <sub>CC</sub>                            |                     | 4.5   | 5   | 5.5 | 4.75  | 5   | 5.25 | v    |

| Normalized fan-out from                                    | High Logic          |       |     |     |       |     |      |      |

| each output, N                                             | Level               |       |     | 20  |       |     | 20   |      |

|                                                            | Low Logic<br>Level  |       |     | 10  |       |     | 10   | •    |

| Input clock frequency, f <sub>Cl</sub>                     | ock                 | 0     |     | 25  | 0     |     | 25   | MHz  |

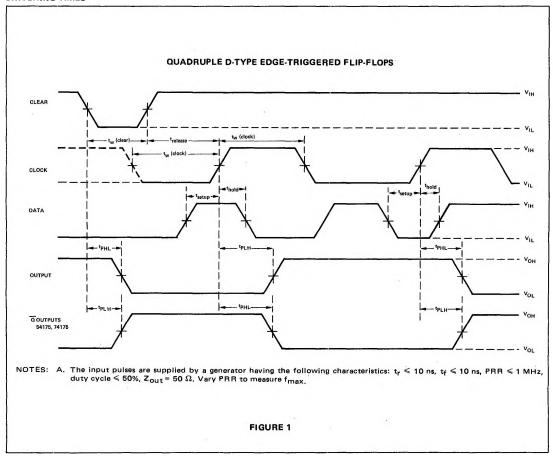

| Width of clock or clear pu<br>(See Figure 1)               | lse, t <sub>W</sub> | 20    |     |     | 20    |     |      | ns   |

| Data setup time, t <sub>setup</sub><br>(See Figure 1)      |                     | 20    |     |     | 20    |     |      | ns   |

| Hold time thold<br>(See Figure 1)                          |                     | 0     |     |     | 0     |     |      | ns   |

| Operating free-air tempera                                 | ture, TA            | -55   | 25  | 125 | o     | 25  | 70   | °c   |

| Clear release setup, t <sub>releas</sub><br>(See Figure 1) | e                   | 25    |     |     | 25    |     |      | ns   |

## ELECTRICAL CHARACTERISTICS (over operating free-air temperature range unless otherwise noted)

|                 |                                             |                                                    |                                                    | 54175 |      | 74175 |     |      |      |      |

|-----------------|---------------------------------------------|----------------------------------------------------|----------------------------------------------------|-------|------|-------|-----|------|------|------|

|                 | PARAMETER                                   | TEST CON                                           | DITIONS                                            | MIN   | TYP‡ | MAX   | MIN | TYP‡ | MAX  | UNIT |

| VIH             | High-level input voltage                    |                                                    |                                                    | 2     |      |       | 2   |      |      | v    |

| VIL             | Low-level input voltage                     | á-                                                 |                                                    |       |      | 0.8   |     |      | 8.0  | v    |

| v <sub>I</sub>  | Input clamp voltage                         | V <sub>CC</sub> = MAX,                             | I <sub>I</sub> = -12 mA                            |       |      | -1.5  |     |      | -1.5 | v    |

| v <sub>он</sub> | High-level output voltage                   | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2 V,<br>I <sub>OH</sub> =-800 μA | 2.4   |      |       | 2.4 |      |      | v    |

| VOL             | Low-level output voltage                    | V <sub>CC</sub> = MIN,<br>V <sub>IL</sub> = 0.8 V, | V <sub>IH</sub> = 2V,<br>I <sub>OL</sub> = 16 mA   |       |      | 0.4   | 1   |      | 0.4  | v    |

| ij              | Input current at maxi-<br>mum input voltage | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 5.5V                              |       |      | 1     |     |      | 1    | mA   |

| ΉΗ              | High-level input current                    | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 2.4 V                             |       |      | 40    |     |      | 40   | μА   |

| IIL             | Low-level input current                     | V <sub>CC</sub> = MAX,                             | V <sub>I</sub> = 0.4 V                             |       |      | -1.6  |     |      | -1.6 | mA   |

| los             | Short-circuit output current §              | V <sub>CC</sub> = MAX                              |                                                    | -20   |      | -57   | -18 |      | -57  | mA   |

| <sup>1</sup> cc | Supply current                              | V <sub>CC</sub> = MAX                              |                                                    |       |      |       |     |      |      |      |

|                 |                                             | Note 1                                             |                                                    |       | 30   | 45    |     | 30   | 45   | mA   |

<sup>§</sup> Not more than one output should be started at a time.

NOTE 1: With all outputs open and 4.5V applied to all data and clear inputs, ICC is measured after a momentary ground, then 4.5V, is applied to clock.

## SWITCHING CHARACTERISTICS, $V_{CC}$ = 5 V, $T_A$ = 25°C, N = 10

| PARAMETER        |                                                                                    | TEST CONDITIONS                             | MIN | TYP | MAX | UNIT |

|------------------|------------------------------------------------------------------------------------|---------------------------------------------|-----|-----|-----|------|

| f <sub>max</sub> | Maximum input clock frequency                                                      |                                             | 25  | 35  |     | MHz  |

| <sup>t</sup> PHL | Propagation delay time, high-to-<br>low-level output Q from clear                  | C <sub>L</sub> = 15 pF R <sub>L</sub> = 400 |     | 23  | 35  | ns   |

| <sup>t</sup> PLH | Propagation delay time low-to-<br>high-level output Q from clear<br>(54175, 74175) |                                             |     | 16  | 25  | ns   |

| tPHL             | Propagation delay time, high-to-<br>low-level output from clock                    |                                             |     | 21  | 30  | ns   |

| tРLН             | Propagation delay time, low-to-<br>high-level output from clock                    |                                             |     | 20  | 30  | ns   |

#### **SWITCHING TIMES**