\$5494-B,F,W • N7494-B,F

# DIGITAL 54/74 TTL SERIES

#### **DESCRIPTION**

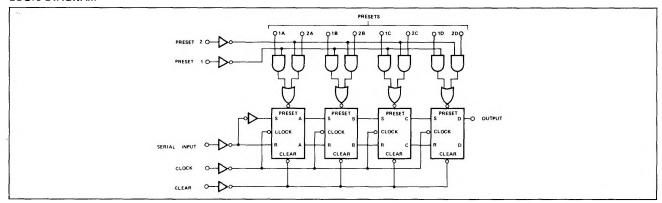

This monolithic shift register, utilizing transistor-transistor logic (TTL) circuits in the familiar Series 74 configuration, is composed of four R-S master-slave flip-flops, four AND-OR-INVERT gates, and four inverter-drivers. Internal interconnections of these functions provide a versatile register which performs right-shift operations as a serial-in, serial-out register or as a dual-source, parallel-toserial converter. A number of these registers may be connected in series to form an n-bit register.

All flip-flops are simultaneously set to the logical 0 state by applying a logical 1 voltage to the clear input. This condition may be applied independent of the state of the clock input, but not independent of state of the preset input. Preset input is independent of the clock and clear states.

The flip-flops are simultaneously set to the logical 1 state from either of two preset input sources. Preset inputs 1A through 1D are activated during the time that a positive pulse is applied to preset 1 if preset 2 is at a logical 0 level. When the logic levels at preset 1 and preset 2 are reversed, preset inputs 2A through 2D are active.

Transfer of information to the outputs occurs when the clock input goes from a logical 0 to a logical 1. Since the flip-flops are R-S master-slave circuits, the proper information must appear at the R-S inputs of each flip-flop prior to the rising edge of the clock input waveform. The serial input provides this information for the first flip-flop. The output of the subsequent flip-flops provide information for the remaining R-S inputs. The clear input, preset 1, and preset 2 must be at a logical 0 when clocking occurs.

This register is completely compatible for use with TTL and DTL logic circuits and when used with other TTL circuits, noise margins are typically one volt. Typical average power dissipation is 175 milliwatts, and propagation delay times from clock to output are typically 25 nanoseconds.

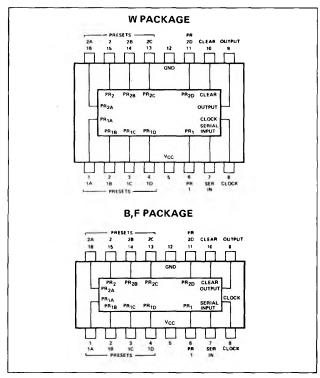

#### **PIN CONFIGURATIONS**

### **LOGIC DIAGRAM**

#### RECOMMENDED OPERATING CONDITIONS

|                                                             | MIN  | TYP | MAX  | UNIT |

|-------------------------------------------------------------|------|-----|------|------|

| Supply Voltage V <sub>CC</sub> (See Note 1): S5494 Circuits | 4.5  | 5   | 5.5  | V    |

| N7494 Circuits                                              | 4.75 | 5   | 5.25 | V    |

| Normalized Fan-Out From Each Output                         |      |     | 10   |      |

| Width of Clock Pulse, tp(clock)                             | 35   |     | }    | ns   |

| Width of Clear Pulse, tp(clear)                             | 30   |     |      | ns   |

| Width of Preset Pulse, tp(preset)                           | 30   |     |      | ns   |

| Serial Input Setup Time: t <sub>setup</sub> (1)             | 35   |     |      | ns   |

| tsetup(0)                                                   | 25   |     |      | ns   |

| Serial Input Hold Time, thold                               | 0    |     |      |      |

## SIGNETICS DIGITAL 54/74 TTL SERIES - S5494 ● N7494

#### ELECTRICAL CHARACTERISTICS (over recommended operating free-air temperature range unless otherwise noted)

| PARAMETER                                  |                                                                                      | TEST CONDITIONS*                                                         |                | MIN        | TYP**       | MAX        | UNIT         |

|--------------------------------------------|--------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------|------------|-------------|------------|--------------|

| V <sub>in(1)</sub>                         | Input voltage required to ensure logical 1 at any input terminal                     | V <sub>CC</sub> = MIN                                                    |                | 2          |             |            | v            |

| V <sub>in</sub> (0)                        | Input voltage required to ensure logical 0 at any input terminal                     | V <sub>CC</sub> = MIN                                                    |                |            |             | 0.8        | V            |

| V <sub>out(1)</sub><br>V <sub>out(0)</sub> | Logical 1 output voltage Logical 0 output voltage                                    | $V_{CC} = MIN, I_{load} = -400 \mu A$<br>$V_{CC} = MIN, I_{sink} = 16mA$ |                | 2.4        | 3.5<br>0.22 | 0.4        | \  \ \ \ \ \ |

| l <sub>in(1)</sub>                         | Logical 1 level input current at any input except preset 1 and preset 2              | $V_{CC} = MAX$ , $V_{in} = 2.4V$<br>$V_{CC} = MAX$ , $V_{in} = 5.5V$     |                |            |             | 40<br>1    | μA<br>mA     |

| lin(1)                                     | Logical 1 level input current at preset 1 and preset 2 Logical 0 level input current | $V_{CC} = MAX, V_{in} = 2.4V$<br>$V_{CC} = MAX, V_{in} = 5.5V$           |                |            |             | 160<br>1   | μA<br>mA     |

| <sup> </sup> in(0)                         | at any input except preset 1 and preset 2                                            | $V_{CC} = MAX, V_{in} = 0.4V$                                            |                |            |             | -1.6       | mA           |

| <sup>1</sup> in(0)                         | Logical 0 level input current at preset 1 and preset 2                               | $V_{CC} = MAX, V_{in} = 0.4V$                                            |                |            |             | -6.4       | mA           |

| los                                        | Short-circuit input current <sup>†</sup>                                             | V <sub>CC</sub> = MAX, V <sub>out</sub> = 0                              | S5494<br>N7494 | -20<br>-18 |             | -57<br>-57 | mA<br>mA     |

| <sup>1</sup> cc                            | Supply current                                                                       | V <sub>CC</sub> = MAX                                                    | S5494<br>N7494 |            | 35<br>35    | 50<br>58   | mA<br>mA     |

# SWITCHING CHARACTERISTICS, $V_{CC}$ = 5V, $T_A$ = 25°C, N = 10

| PARAMETER         |                               | TEST CONDITIONS        |                       | MIN | TYP | MAX | UNIT |

|-------------------|-------------------------------|------------------------|-----------------------|-----|-----|-----|------|

| 1 <sub>max</sub>  | Maximum clock frequency       | C <sub>L</sub> = 15pF, | R <sub>L</sub> = 400Ω | 10  |     |     | MHz  |

|                   | Propagation delay time to     |                        |                       |     |     |     |      |

| t <sub>pd1</sub>  | logical 1 level from clock to | $C_L = 15pF$ ,         | $R_L = 400 \Omega$    |     | 25  | 40  | ns   |

|                   | output to output              |                        |                       | 1   |     |     |      |

|                   | Propagation delay time to     |                        |                       |     |     |     |      |

| t <sub>pd</sub> 0 | logical 0 level from clock to | C <sub>L</sub> = 15pF, | $R_L = 400\Omega$     |     | 25  | 40  | ns   |

| ,                 | output                        |                        |                       |     |     |     |      |

|                   | Propagation delay time to     |                        |                       |     |     |     |      |

| <sup>t</sup> pd1  | logical 1 level from preset   | $C_L = 15pF$ ,         | $R_L = 400 \Omega$    |     |     | 35  | ns   |

|                   | to output                     | _                      |                       |     |     |     |      |

|                   | Propagation delay time to     |                        |                       |     |     |     |      |

| t <sub>pd</sub> 0 | logical 0 level from clear to | $C_L = 15pF$ ,         | $R_L = 400 \Omega$    |     |     | 40  | ns   |

|                   | output                        | _                      | _                     |     |     |     |      |

<sup>\*</sup> For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable

<sup>\*\*</sup> All typical values are at V<sub>CC</sub> = 5V, T<sub>A</sub> = 25°C.

† Not more than one output should be shorted at a time.